SAP

数据结构

spring boot

kotlin

Table API

pycharm

教育电商

科技

mongodb

数据可视化

位置编码

camera

数据导出

自回归

下载视频

misc-1

盒子模型

RBF神经网络

高等数学

dmidecode

PCIE

2024/4/30 18:53:52PCIe总线基本概念

前言:

PCI Express(Peripheral Component Interconnect Express),简称PCIe,是一种高速串行计算机扩展总线标准,用于将主板与多种硬件设备连接起来。它是由PCI-SIG开发的,旨在取代旧的PCI、PCI-…

rk3568 适配PCIE(一)

rk3568 适配pcie2.0

PCIe(Peripheral Component Interconnect Express)总线是一种用于连接计算机主板和外部设备的高速串行总线接口。它取代了传统的PCI和PCI-X总线,并提供了更高的带宽和性能。PCIe总线通常用于连接诸如显卡、网卡、存储控制器等设备。 PCIe总线具有以下特…

[SSD科普之2] SATA、mSATA、M.2、M.2(NVMe)、PCIE固态硬盘接口详解

固态硬盘概念固态驱动器(Solid State Drive),俗称固态硬盘,固态硬盘是用固态电子存储芯片阵列而制成的硬盘,因为台湾英语里把固体电容称之为Solid而得名。SSD由控制单元和存储单元(FLASH芯片、DRAM芯片&…

RK356x U-Boot研究所(命令篇)3.7 pci与nvme命令的用法

平台U-Boot 版本Linux SDK 版本RK356x2017.09v1.2.3文章目录 一、设备树与config配置二、pci命令的定义三、nvme命令的定义四、pci与nvme命令的用法3.1 pci总线扫描3.2 nvme设备信息3.3 nvme设备读写一、设备树与config配置

RK3568支持PCIe接口,例如ROC-RK3568-PC: 原理图如…

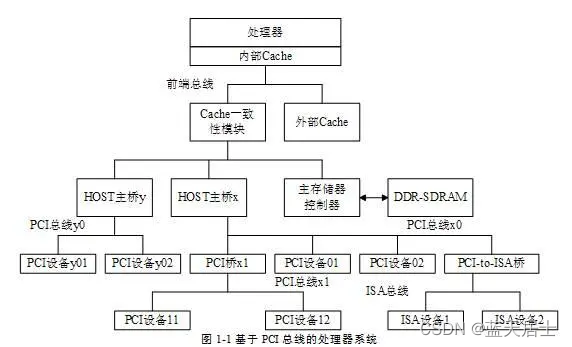

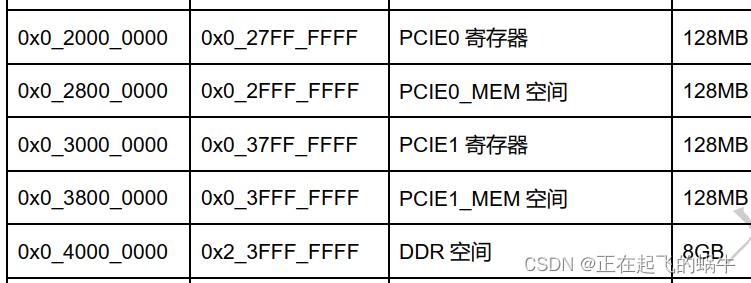

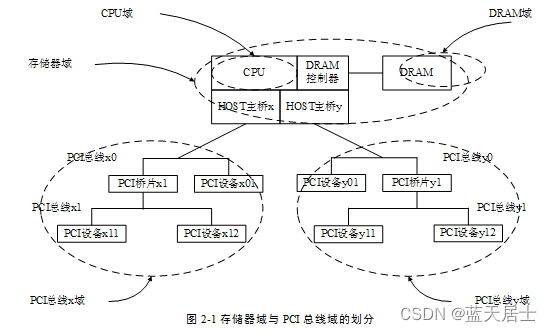

PCI/PCIE总线的宏观理解

1、pcie总线协议实现的效果 (1)像访问内存一样去访问外设; (2)当建立好CPU地址空间到PCI/PCIE地址空间的映射关系后,程序访问CPU地址空间就可以达到访问PCI/PCIE地址空间的效果; 2、芯片地址空间 (1)32位的CPU寻址范围是4G,64位的…

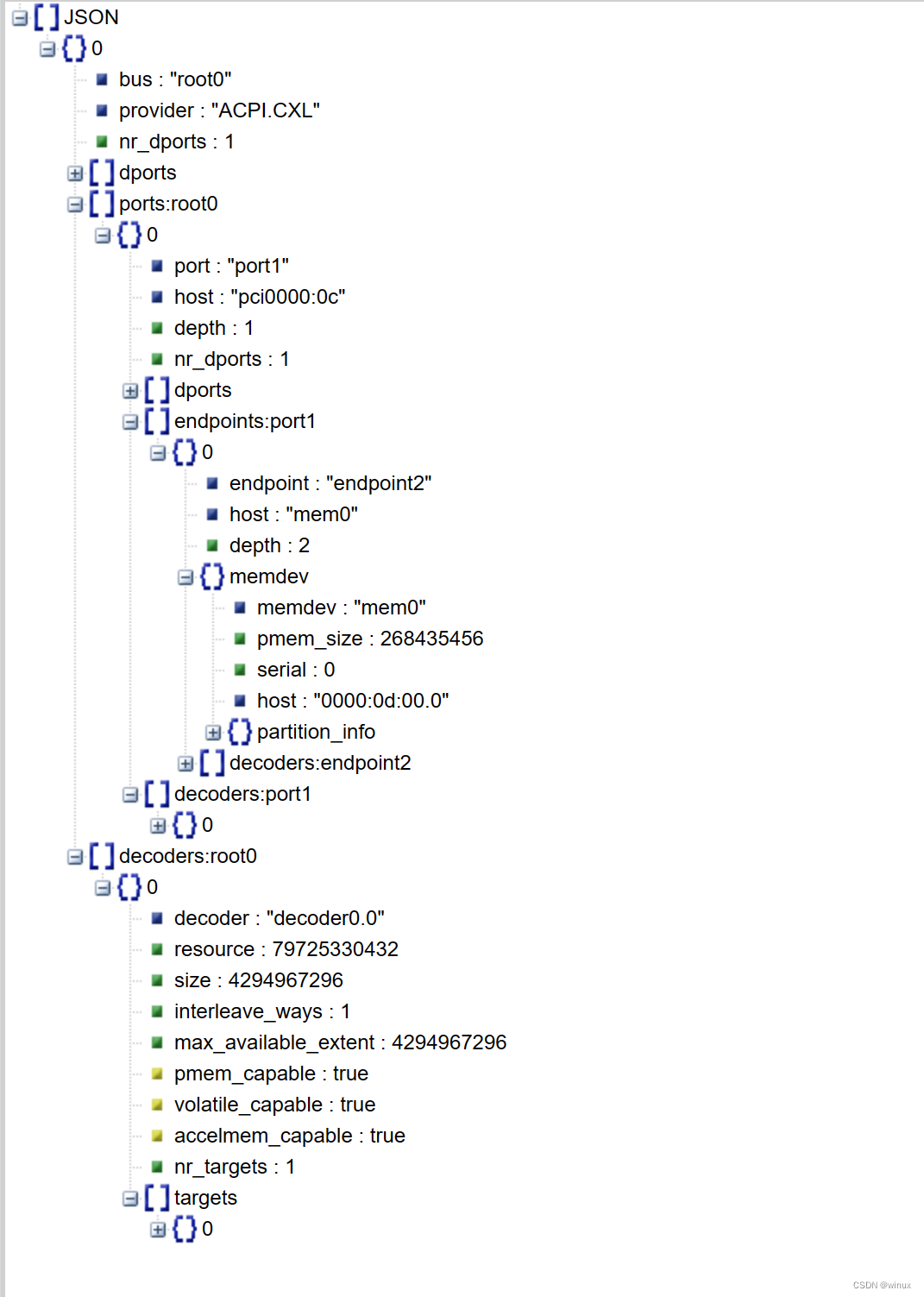

使用qemu模拟CXL.mem设备

CXL可以说是自PCIe技术诞生几十年以来最具变革性的新技术了。可以想象有了CXL以后机箱的边界将被彻底打破,服务器互相使用对方的内存,网卡,GPU 。整个机架甚至跨机架的超级资源池化成为可能,云计算也将进入一个新的时代。

当前In…

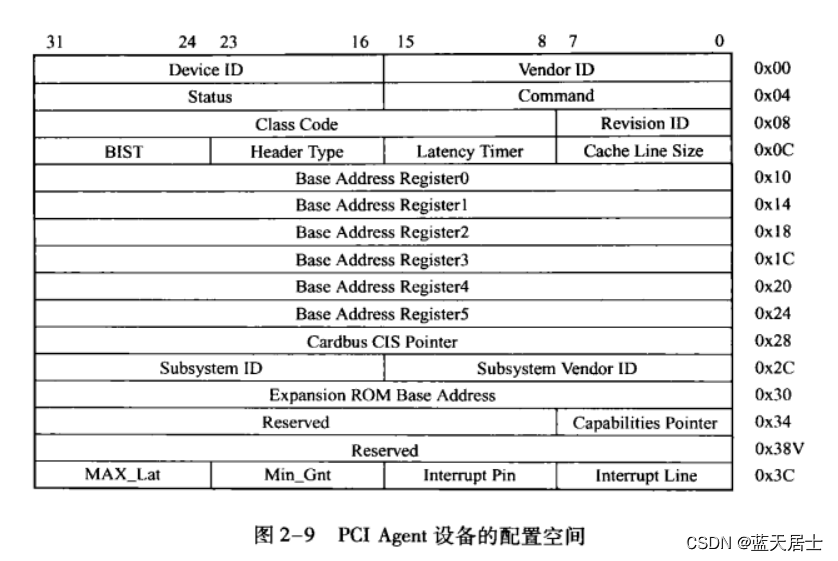

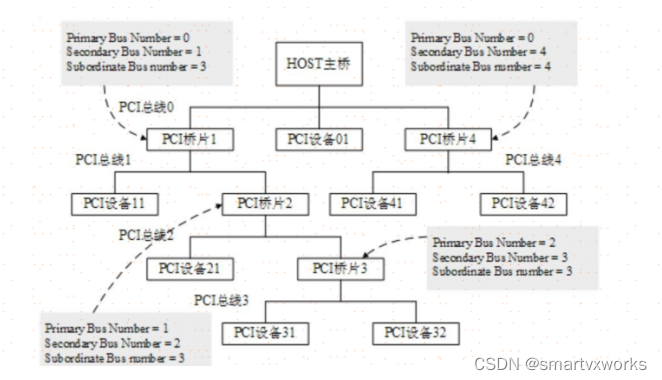

《PCI Express体系结构导读》随记 —— 第I篇 第2章 PCI总线的桥与配置(15)

接前一篇文章:《PCI Express体系结构导读》随记 —— 第I篇 第2章 PCI总线的桥与配置(14) 2.3.1 PCI桥

在PCI Agent设备的配置空间中包含了许多寄存器,这些寄存器决定了该设备在PCI总线中的使用方法,本节不会全部介绍…

[RK-Linux] RK3399支持M.2 NVMe SSD启动

延续《[RK-Linux] 从主线U-Boot移植PCIe及其PHY驱动到RK3399 U-Boot》 启动流程:

maskrom -> loader(从 eMMC 存储器加载) -> u-boot(从 eMMC 存储器加载)-> kernel (从 M.2 NVMe SSD 加载)-> rootfs (从 M.2 NVMe SSD 挂载)配置从 M.2 NVMe SSD 启动: …

[RK-Linux] 从主线U-Boot移植PCIe及其PHY驱动到RK3399 U-Boot

rk3399 u-boot 并没有支持 pcie 及其 phy 驱动,但是上游代码有支持。这里通过从上游 v2024.01-rc3 分支移植这部分驱动到 rk u-boot。

通过 rk3399.dtsi 知道 pci 匹配项为 rockchip,rk3399-pcie:

pcie0: pcie@f8000000 {compatible = "rockchip,rk3399-pcie";..…

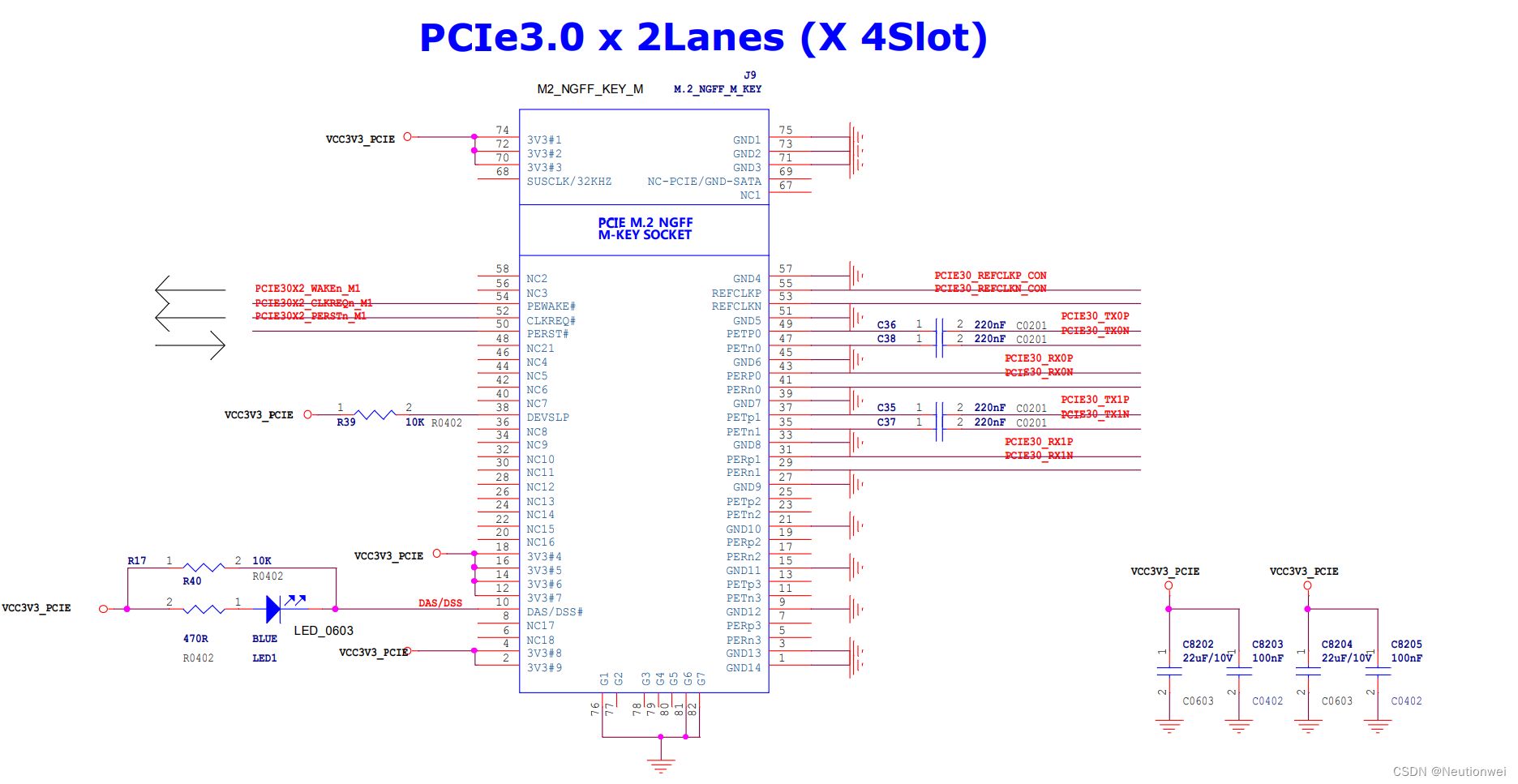

[RK-Linux] 移植Linux-5.10到RK3399(五)| 检查PCIe并识别M.2 NVMe SSD

ROC-RK3399-PC Pro 引出了 PCIe 座子,用于装载 M.2 NGFF M-Key 接口的 SSD。 文章目录 一、PCIe二、NVMe三、调试一、PCIe

PCIe(Peripheral Component Interconnect Express)是一种高速串行总线接口,用于连接计算机系统中的各种外部设备。它是传统PCI总线的进化版本,提供…

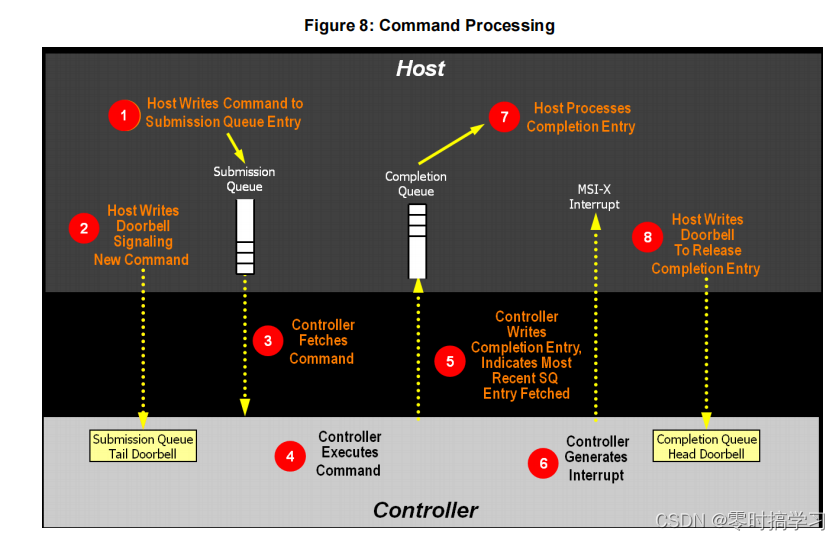

[NVMe 协议] PCIe 和 NVME 寄存器

声明 主页:元存储的博客_CSDN博客 依公开知识及经验整理,如有误请留言。 个人辛苦整理,付费内容,禁止转载。 内容摘要 前言

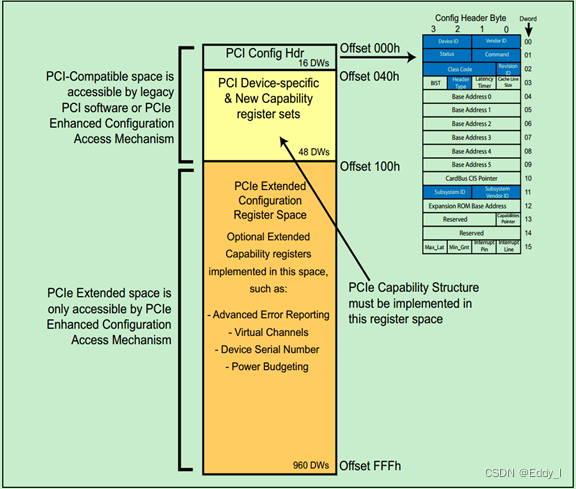

NVMe(Over PCIe)寄存器主要分为两类,一类是PCIe配置空间寄存器,一类是NVMe控制器相关的寄存器。 NVMe离不开PCIe,NVMe SSD是PCIe的endpoint。…

高级FPGA开发之基础协议PCIe(二)

高级FPGA开发之基础协议之PCIe(二)

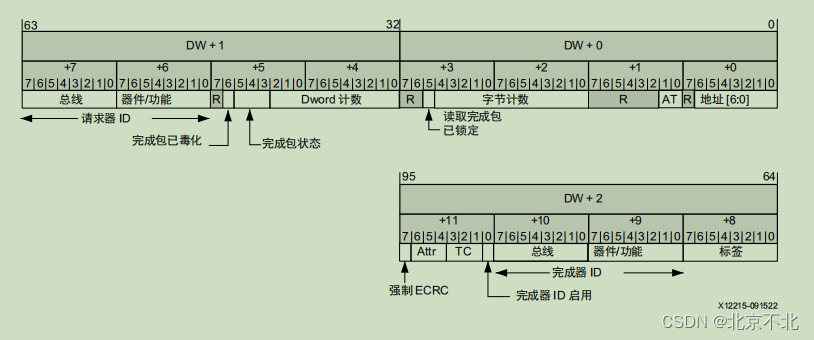

一、TLP报文类型

在PCIe总线中,存储器读写、I/O读写和配置读写请求TLP主要由以下几类报文组成: 1.1 存储器读请求TLP和读完成TLP

当PCIe主设备(RC或者EP)访问目标设备…

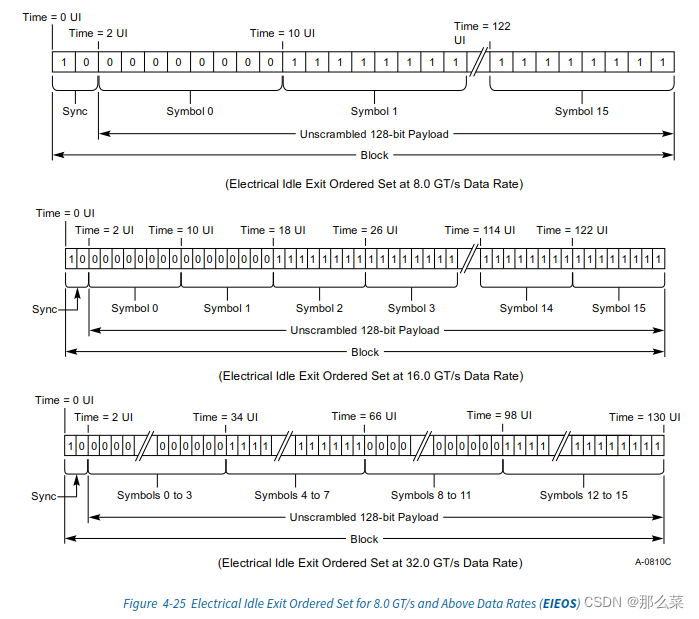

S4.2.4.3 Electrical Idle Sequence(EIOS)

一 本章节主讲知识点

1.1 EIOS的具体码型

1.2 EIOS的识别规则

1.3 EIEOS的具体码型

二 本章节原文翻译

当某种状态下,发送器想要进入电器空闲状态的时候,发送器必须发送EIOSQ,也既是:电器Electrical Idle Odered Set Sequenc…

《PCI Express体系结构导读》随记 —— 第I篇 第2章 PCI总线的桥与配置(1)

前言中曾提到:本章重点介绍PCI桥。

在PCI体系结构中含有两类桥:一类是HOST主桥;另一类是PCI桥。在每一个PCI设备中(包括PCI桥),都含有一个配置空间。这个配置空间由HOST主桥管理,而PCI桥可以转…

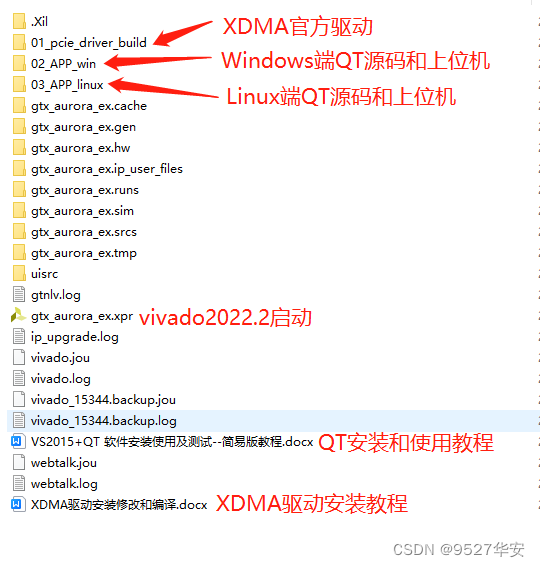

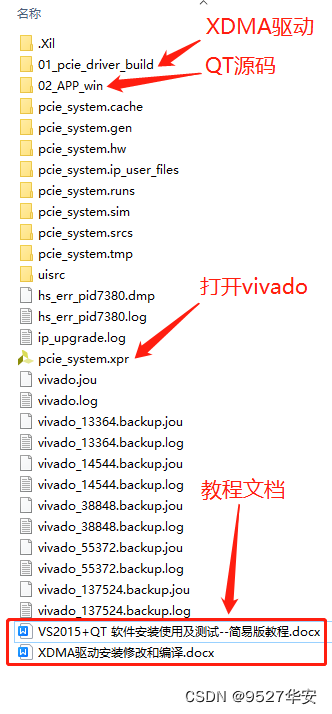

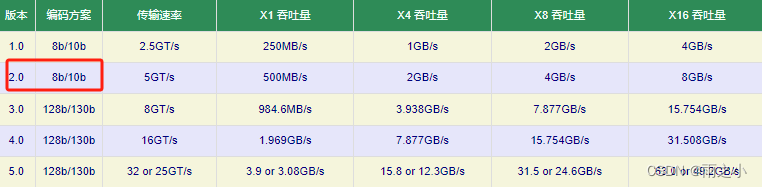

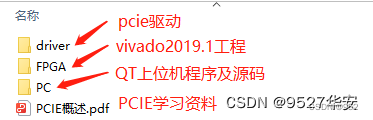

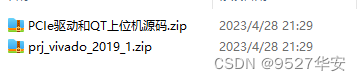

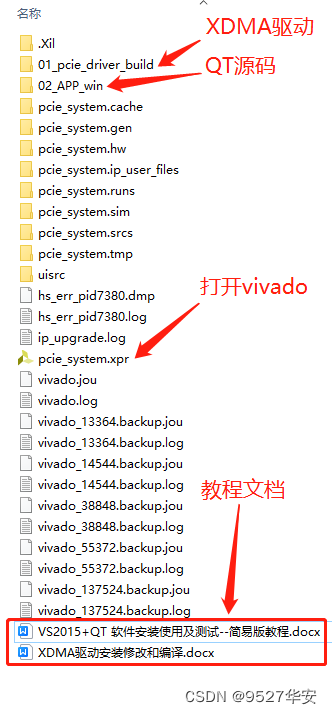

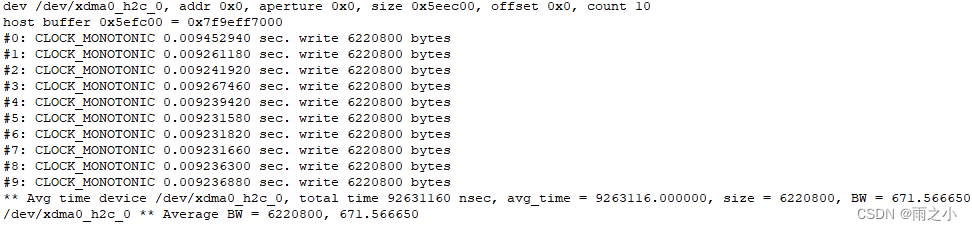

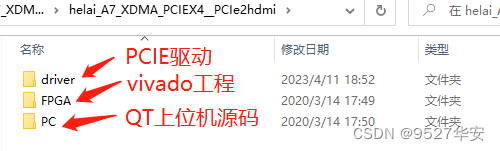

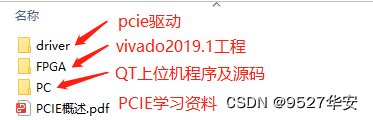

FPGA基于XDMA实现PCIE X8视频采集HDMI输出 提供工程源码和QT上位机程序和技术支持

目录 1、前言2、我已有的PCIE方案3、PCIE理论4、总体设计思路和方案5、vivado工程详解6、驱动安装7、QT上位机软件8、上板调试验证9、福利:工程代码的获取 1、前言

PCIE(PCI Express)采用了目前业内流行的点对点串行连接,比起 PC…

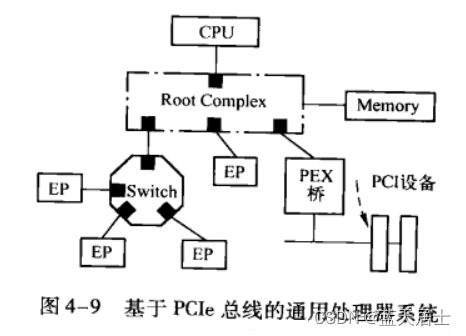

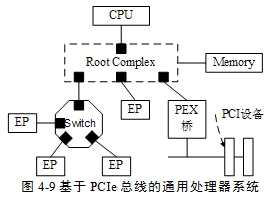

PCIe总线中Root Complex(RC)

在不同的处理器系统中,RC的实现有较大差异。PCIe总线规范并没有规定RC的实现细则。在有些处理器系统中,RC相当于PCIe主桥,也有的处理器系统也将PCIe主桥称为PCIe总线控制器。而在x86处理器系统中,RC除了包含PCIe总线控制器之外&am…

rk3568 适配PCIE(二)

rk3568 适配pcie3.0

PCIe(Peripheral Component Interconnect Express)是一种用于连接计算机主板和其他设备的高速串行总线接口。PCIe 2.0和PCIe 3.0是两个不同版本的PCIe规范,它们在以下几个方面有所不同: 带宽:PCIe 2.0的理论带宽为每条通道5 Gbps,而PCIe 3.0的理论带…

FPGA基于XDMA实现PCIE X8的HDMI视频采集 提供工程源码和QT上位机程序和技术支持

目录 1、前言2、我已有的PCIE方案3、PCIE理论4、总体设计思路和方案5、vivado工程详解6、驱动安装7、QT上位机软件8、上板调试验证9、福利:工程代码的获取 1、前言

PCIE(PCI Express)采用了目前业内流行的点对点串行连接,比起 PC…

3: PCIe BDF(Bus,Device,Function)

目录

1.概述

2.BUS:总线号

3.Device:设备号

4.Function:功能号 1.概述 PCIe总线中的每一个功能都有一个唯一的标识符与之对应。这个标识符就是BDF(Bus,Device,Function) 2.BUS:总…

【PCIE系统学习】Gen1/2Gen3/4 symobl与OrderSet概念对比

这个专栏要干的事:学习PCIE理论知识,学会PCIE IP/VIP的使用。可以达到上手做项目,而不是空有理论

适合谁看:正在学习PCIE 设计验证,但学的过于零散。想有对比的系统的学习。 低价收费的目的:抵制胡乱传播转载现象。

版本控制:便于增加内容以及勘误 版本说明v20230829 …

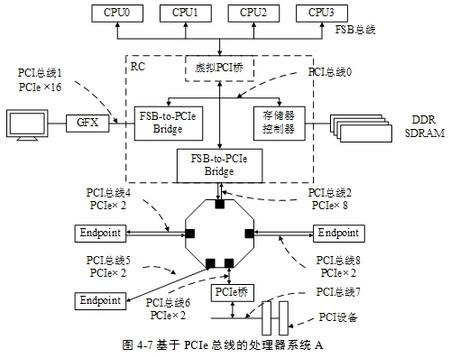

PCIe架构的处理器系统介绍

不同的处理器系统中,PCIe体系结构的实现方式不尽相同。PCIe体系结构以Intel的x86处理器为蓝本实现,已被深深地烙下x86处理器的印记。在PCIe总线规范中,有许多内容是x86处理器独有的,也仅在x86处理器的Chipset中存在。在PCIe总线规…

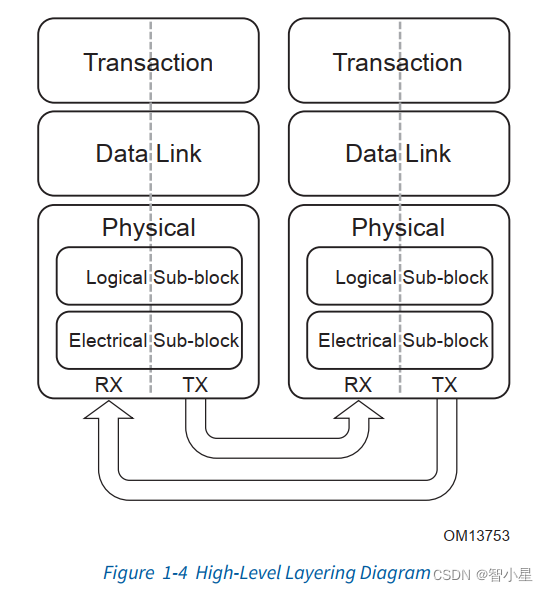

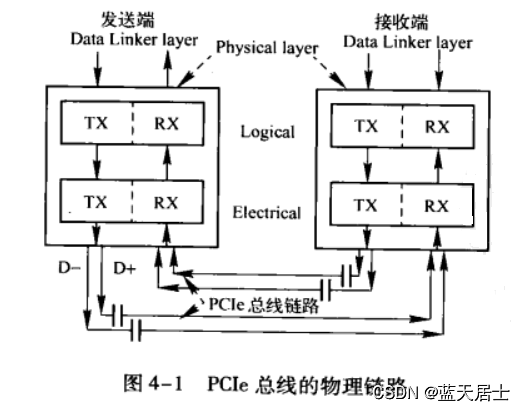

《PCI Express体系结构导读》随记 —— 第II篇 第4章 PCIe总线概述(8)

接前一篇文章:《PCI Express体系结构导读》随记 —— 第II篇 第4章 PCIe总线概述(7) 4.1 PCIe的基础知识

与PCI总线不同,PCIe总线使用端到端的连接方式,在一条PCIe链路的两端只能各连接一个设备,这两个设备…

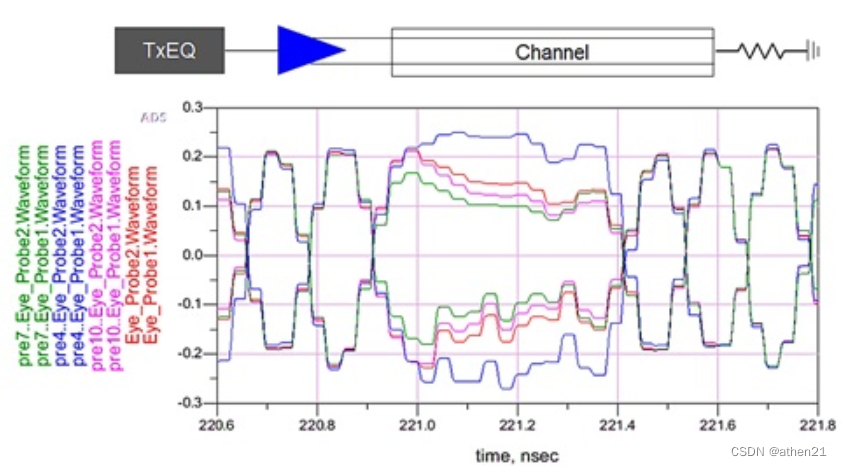

如何确保PCIe Gen3通道的信号质量

PCIe 3.0设计面对的挑战

PCIe由PCI-SIG协会研发和维护的一个高速标准接口,PCIe3.0是其开发的第三代接口高速差分接口,其单个差分对信号速率可到达8.0Gbps,目前其以广泛的应用于计算机服务器等设备领域。

下图显示的是一个典型的PCIe Gen3的…

【Linux驱动】驱动设计硬件基础----串口、I2C、SPI、以太网接口、PCIE

1.前言

常见的外设接口与总线的工作方式,包括串口、I2C、SPI、USB、以太网接口、PCI和PCI-E、SD和SDIO等。

2.串口

RS-232、RS-422与RS-485都是串行数据接口标准,最初都是由电子工业协会(EIA)制订并发布的。

3.I2C

I2C&…

PCIe 3.0软核控制器,具备AXI接口和DMA功能

PCIe-AXI-Controller

PCIe-AXI-Controller兼容PCI Express Base Specification Revision 3.1,实现PCIe PHY Layer,Data Link Layer以及Transaction Layer的所有功能特性,不仅内置DMA控制器,而且具备AXI4用户接口,提供…

PCIE1—快速实现PCIE接口上下位机通信(一)

1.简介 PCI Express(PCIE)是一种高速串行总线标准,广泛应用于计算机系统中,用于连接主板和外部设备。在FPGA领域中,PCIE也被广泛应用于实现高速数据传输和通信。FPGA是一种灵活可编程的集成电路,可以根据需…

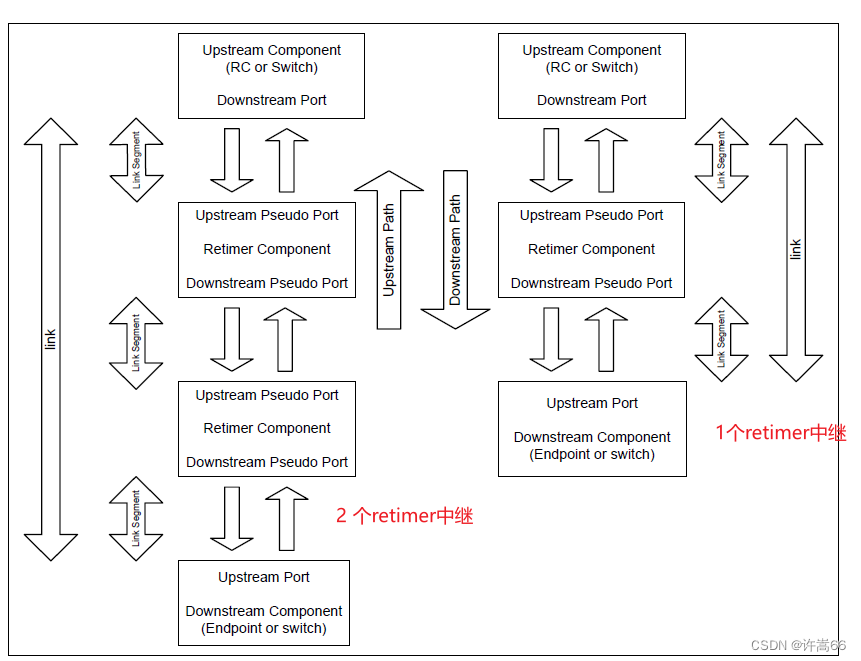

PCIE Retimer

1 Retimers retimer是一种PCIE的扩展设备,用于长距离高效地传输数据,起到一种中继器的作用。PCIe扫盲——ReTimer和ReDriver简介 在EP和RC中间最多允许两级retimers级联,其可以分为纯模拟类,它是一种对物理层协议无关的芯片&…

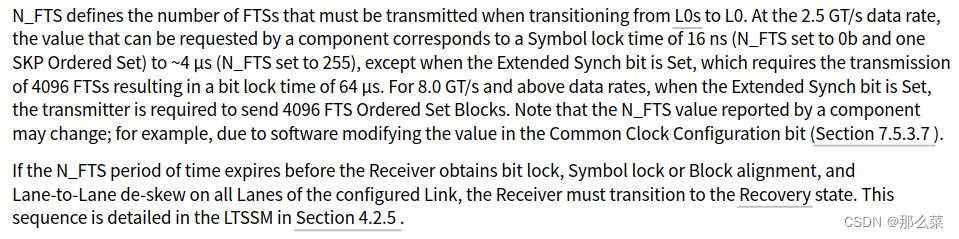

S4.2.4.5 Fast Training Sequence (FTS)

一 本章节主讲知识点

1.1 FTS的用途和实现注意

二 本章节原文翻译

Fast Training Sequence (FTS) 主要用于在L0s->L0跳转的过程中,让Receiver 检测到电气空闲退出,以及实现bit 和 symbol lock。

2.1 Gen1 and Gen2 速率

对于Gen1/2 FTS的组成如下…

[SSD科普之1] PCIE接口详解及应用模式

PCI-Express(peripheral component interconnect express)是一种高速串行计算机扩展总线标准,它原来的名称为“3GIO”,是由英特尔在2001年提出的,旨在替代旧的PCI,PCI-X和AGP总线标准。一、PCI-E x1/x4/x8/x16插槽模式PCI-E有 x1/…

FPGA GTH aurora 8b/10b编解码 PCIE 视频传输,提供2套工程源码加QT上位机源码和技术支持

目录 1、前言免责声明 2、我这里已有的 GT 高速接口解决方案3、GTH 全网最细解读GTH 基本结构GTH 发送和接收处理流程GTH 的参考时钟GTH 发送接口GTH 接收接口GTH IP核调用和使用 4、设计思路框架视频源选择silicon9011解码芯片配置及采集动态彩条视频数据组包GTH aurora 8b/10…

《PCI Express体系结构导读》随记 —— 第I篇 第1章 PCI总线的基本知识(15)

接前一篇文章:《PCI Express体系结构导读》随记 —— 第I篇 第1章 PCI总线的基本知识(14) 1.3 PCI总线的存储器读写总线事务 1.3.4 PCI读写主存储器

前文已提到,由于本节内容较长,因此将后一部分内容放在本文中。

为…

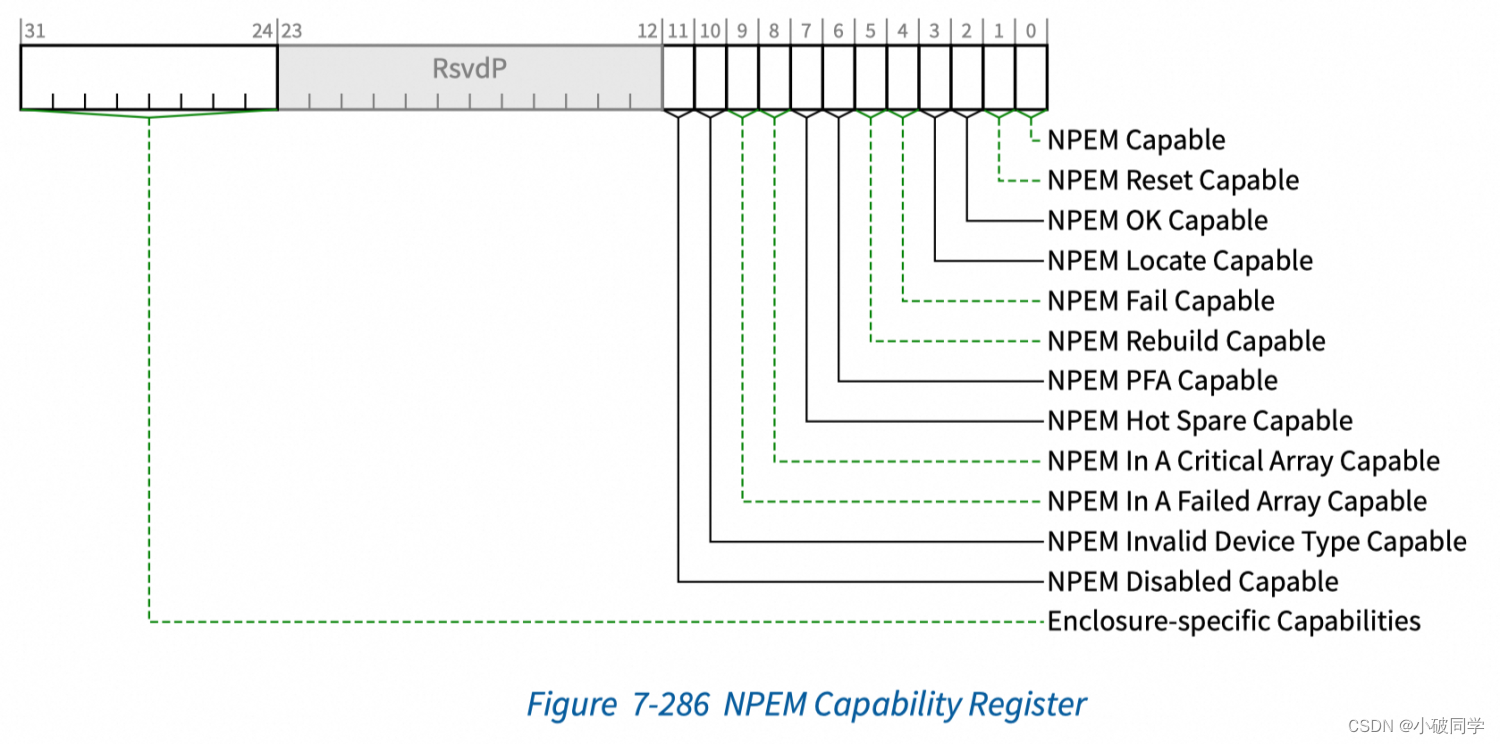

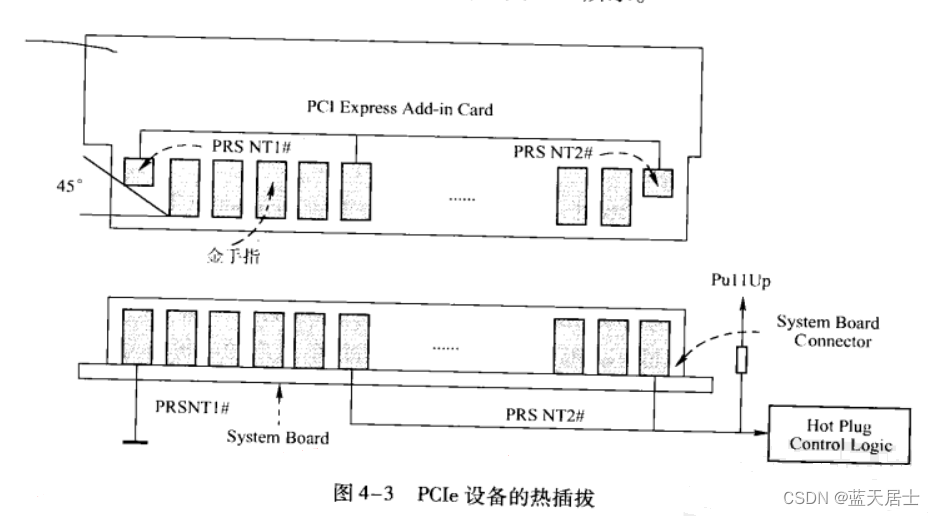

PCIe学习笔记(1)Hot-Plug机制

文章目录 Hot-Plug InitHot Add FlowSurprise Remove FlowNPEM Flow Hot-Plug Init

PCIe hot-plug是一种支持在不关机情况下从支持的插槽添加或删除设备的功能,PCIe架构定义了一些寄存器以支持原生热插拔。相关寄存器主要分布在Device Capabilities, Slot Capabili…

Jetson Orin平台pcie vnet关于DMA操作问题调试

前言有个问题关于pcie vnet nvdia/drivers/pci/endpoint/functions/pci-epf-tegra-vnet.c function:

static netdev_tx_t tvnet_ep_start_xmit(struct sk_buff *skb,

struct net_device *ndev)/* Trigger DMA write from src_iova to dst_iova */desc_widx = desc_cnt->wr_…

FPGA纯verilog实现RIFFA的PCIE测速实验,提供工程源码和QT上位机

目录1、前言2、RIFFA理论基础3、vivado工程详解4、上板调试验证并演示QT上位机源代码QT源代码解析5、福利:工程代码的获取1、前言

PCIE是目前速率很高的外部板卡与CPU通信的方案之一,广泛应用于电脑主板与外部板卡的通讯,PCIE协议极其复杂&a…

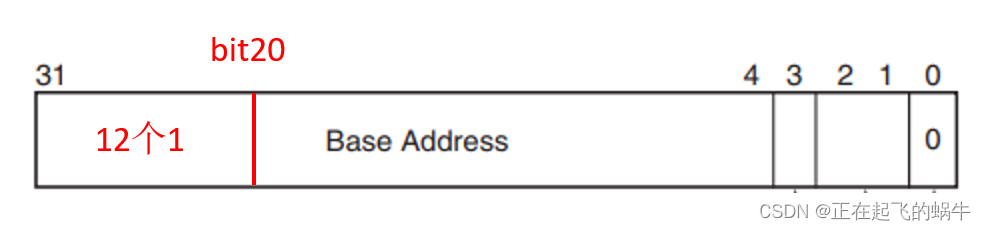

如何识别PCI/PCIE设备需要申请多大的地址空间?

1、PCI/PCIE设备的配置空间 (1)PCI/PCIE设备需要的资源都在配置空间里进行指定,其中需要的地址空间资源在配置空间的基地址寄存器里指定; (2)参考博客:《PCI设备和PCI桥的配置空间(header_type0、header_type1)和配置命令(type0、type1)详解》…

PCI-Express1.0总带宽计算

知识点一:两个PCI-Express设备之间可能的通路数为1、2、4、8、16、32

知识点二:PCI-Express x n 表示具有n个通路的PCI-Express链路。

知识点三:PCI-Express总线采用串行传输方式

知识点四:在发送和接收过程中,每个…

PCI-Express1.0总带宽计算

知识点一:两个PCI-Express设备之间可能的通路数为1、2、4、8、16、32

知识点二:PCI-Express x n 表示具有n个通路的PCI-Express链路。

知识点三:PCI-Express总线采用串行传输方式

知识点四:在发送和接收过程中,每个…

基于XDMA 中断模式的 PCIE 上位机与FPGA数据交互架构 提供工程源码和QT上位机源码

目录 1、前言2、我已有的PCIE方案3、PCIE理论4、总体设计思路和方案图像产生、发送、缓存数据处理XDMA简介XDMA中断模式图像读取、输出、显示QT上位机及其源码 5、vivado工程详解6、上板调试验证7、福利:工程代码的获取 1、前言

PCIE(PCI Express&#…

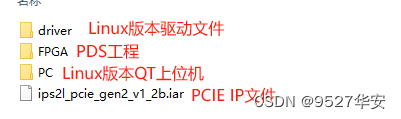

紫光同创FPGA实现PCIE测速试验,提供PDS工程和Linux QT上位机源码和技术支持

目录 1、前言免责声明 2、我这里已有的 GT 高速接口解决方案3、设计思路框架PCIE硬件设计PCIE IP核添加和配置驱动文件和驱动安装QT上位机和源码 4、PDS工程详解5、上板调试验证并演示6、福利:工程代码的获取 紫光同创FPGA实现PCIE测速试验,提供PDS工程和…

PCIe 5.0验证实战,经常遇到的那些问题?

PCIe 5.0是当前最新的PCI Express规范,提供了更高的数据传输速率和更大的带宽。

PCIe是连接两个芯片的接口,负责两个芯片通信, 连接芯片的通路为高速SerDes, 称之为链路。PCIe确保通路正常-链路训练状态机。PCIe在芯片内部是非常重要的一个大的模块&…

PCIE 4.0 Equalizaiton(LTSSM 均衡流程)

1. 均衡

在Tx端有FFE(Feed Forward Equalizer,前馈均衡器);在Rx端有:CTLE(Continuous Time Linear Equalizer,连续时间线性均衡器)和DFE(Decision Feedback Equalizer&a…

PCIe和IIO问题Debug手册

目录说明

第一章 引言. 主要介绍本Debug手册的范围和如何使用本Debug手册;第二章 PCIe和IIO问题分类. 本章主要用于对PCIe和IIO问题分类。文中提供了参考的Debug流程图,以便减少PCIe和IIO问题。

《PCI Express体系结构导读》随记 —— 第II篇 第4章 PCIe总线概述(11)

接前一篇文章:《PCI Express体系结构导读》随记 —— 第II篇 第4章 PCIe总线概述(10) 4.2 PCIe体系结构的组成部件

PCIe总线作为处理器系统的局部总线,其作用与PCI总线类似,主要目的是为了连接处理器系统中的外部设备…

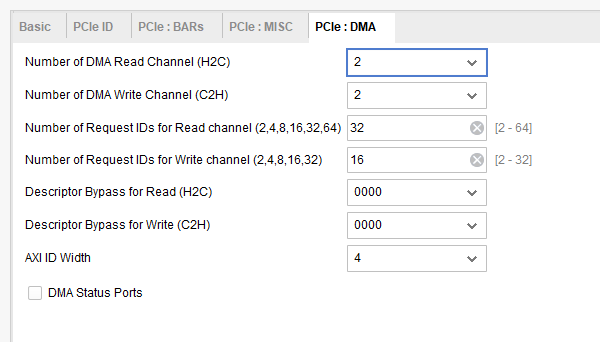

高级FPGA开发之PCIe IP Core(三)

高级FPGA开发之PCIe IP Core(三)

一、PCIe IP核简介

通过阅读PCIe spec文档,可以看到UltraScale器件Integrated Block For PCI Express解决方案IP核是具备高带宽、高可缩放性和高可靠串行互联的解决方案,适用于UltraScale器件。赛灵思在 UltraScale 架…

PCIE知识点-012:PCIE Zero-Length read

1、Zero-Length Write

PCIe协议提出了zero-length的读写操作,并且做了如下说明

Zero-Length Write的含义 A Memory Write Request of 1 DW with no bytes enabled, 即Memory Write 类型tlp中只有1DW的data,且length字段为1,并且tlp header中…

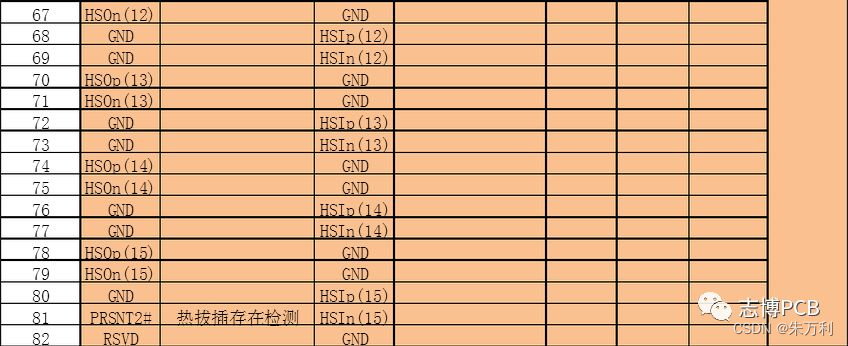

PCIE总线基本介绍(和PCI总线差异、速率计算、引脚定义)

1、PCI和PCIE的差异 (1)PCIE协议在软件编程上是兼容PCI协议,不同在于PCIE和PCI的控制器; (2)PCIE是差分串行信号线,PCI是电平并行信号线; (3)PCI协议使用INTA#、INTB#、INTC#、INTD#四根中断线来触发终端,PCIE协议没有…

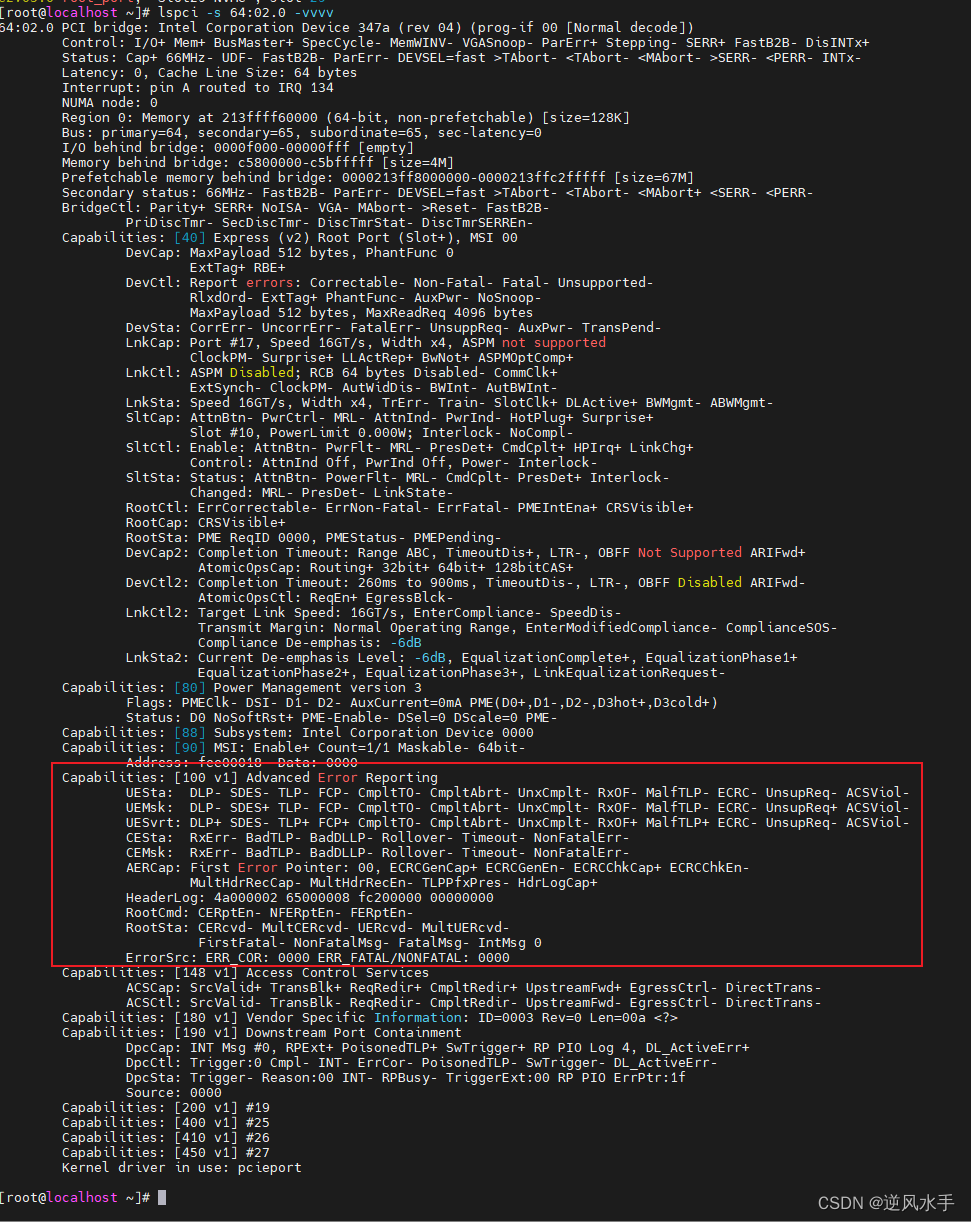

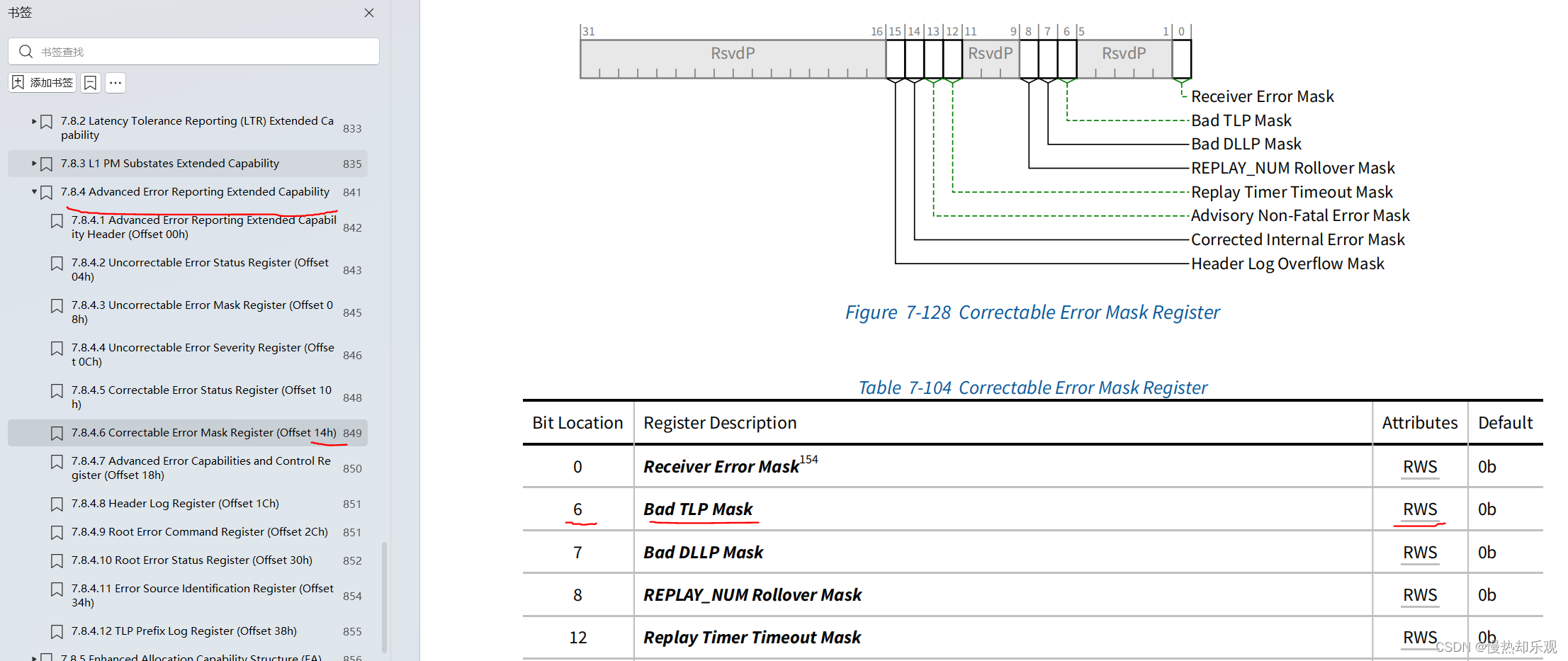

PCIe的capability扩展空间字段解释

解释

这是一段关于高级错误报告的信息,其中包含多个字段和值。以下是每个字段的详细解释:

Capabilities: [100 v1] Advanced Error Reporting 这是该设备支持高级错误报告的能力标识符。 UESta: DLP- SDES- TLP- FCP- CmpltTO- CmpltAbrt- UnxCmplt- R…

#Day Day Plan# 《NCB_PCI_Express_Base 5.0.1.0》pdf 译文笔记

目录

第4章 Physical Layer Logic Block

S4.1 Introduction

S4.2 Logical sub-block

S4.2.4 Link Initialization and Traning

解释PCIe MSI 中断要求中断向量连续?PCIe 规范里并没有明确指出

MSI 向量必须连续?

前言

MSI 物理条件,MSI 中断产生的逻辑是RC初始化的时候,由软件将配置写入到 EP 的 2 个寄存器中,这两个寄存器一个指示的是地址 Message Address,一个指示的是数据 Message Data。当 EP 试图触发…

HI3559AV100和FPGA 7K690T的PCIE接口调试记录-续

上文https://blog.csdn.net/fzktongyong/article/details/134963814?spm1001.2014.3001.5501 上一篇文中PCIE实测速度和理论计算有较大偏差,经过尝试后有所提升。

1、提升效果 1)、RC写操作,实测速度817MB/s(410407&…

FPGA实现SDI视频解码PCIE传输 提供工程源码和QT上位机源码加技术支持

目录 1、前言2、我已有的SDI编解码方案3、我已有的PCIE方案4、总体设计思路和方案SDI摄像头Gv8601a单端转差GTX解串SDI解码VGA时序恢复YUV转RGB图像缓存PCIE发送通路SDI同步输出通路 5、vivado工程详解6、驱动安装7、QT上位机软件8、上板调试验证SDI同步HDMI输出验证PCIE输出验…

zynq基于XDMA实现PCIE X8视频采集HDMI输出 提供工程源码和QT上位机程序和技术支持

目录 1、前言2、我已有的PCIE方案3、基于zynq架构的PCIE4、总体设计思路和方案视频输入通路PCIE数据缓存通路视频输出通路 5、vivado工程详解6、SDK 工程详解7、驱动安装8、QT上位机软件9、上板调试验证10、福利:工程代码的获取 1、前言

PCIE(PCI Expre…

FPGA XDMA 中断模式实现 PCIE X8 测速试验 提供工程源码和QT上位机源码

目录 1、前言2、我已有的PCIE方案3、PCIE理论4、总体设计思路和方案XDMA简介XDMA中断模式QT上位机及其源码 5、vivado工程详解6、上板调试验证7、福利:工程代码的获取 1、前言

PCIE(PCI Express)采用了目前业内流行的点对点串行连接…

FPGA XDMA 中断模式实现 PCIE X8 上位机视频传输 提供工程源码和QT上位机源码

目录 1、前言2、我已有的PCIE方案3、PCIE理论4、总体设计思路和方案图像产生、发送、缓存XDMA简介XDMA中断模式图像读取、输出、显示QT上位机及其源码 5、vivado工程详解6、上板调试验证7、福利:工程代码的获取 1、前言

PCIE(PCI Express)采…

PCI Express架构概述

1. PCIe 总线概述 PCIe(Peripheral Component Interconnect Express)是一种用于连接计算机内部硬件设备的高速串行总线。它是在PCI(Peripheral Component Interconnect)总线的基础上发展而来的。PCI总线是在1992年由Intel推出的&a…

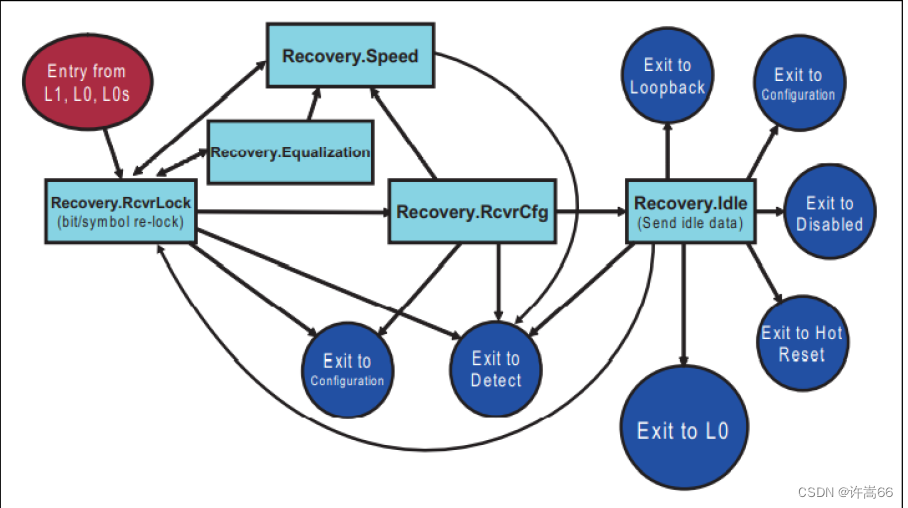

【PCIe】链路LTSSM状态机

1.Power Management

1.1.概述

PCIe的Power Management(PM)分为两种:

PCI-Compatible PM: 符合PCI协议的电源管理,由软件通过Configuration Requests发起;

Active State Power Management(ASPM):定义基于硬件控制的电源管理,同时定义了唤醒系统的机制,PME message机…

S4.2.4.5 Lane Polarity Inversion

一 本章节主讲知识点

1.1 Polarity Inversion 极性反转

1.2 Lane Reversal 通道翻转

二 本章节原文翻译

2.1 极性反转

原文摘录: PCIe 协议规定,必须支持该特性。该特性的目标也是为了简化 PCB 的布线。每个 lane 都包含一组发送(Tx&…

快速由PCI迁移到PCIe

快速由PCI迁移到PCIe

1. 首先要搞清楚两者的一些对应关系

PCI的并行总线 --> PCIe的串行总线

HOST还是那个HOST

HOST桥 --> RC

PCI Agent --> EP

PCI桥 --> Switch

其它诸如配置空间、可预取/不可预取、配置空间的ID寻址、内存及IO空间的地址寻址…

Linux PCI和PCIe总线

1 PCIe中断 - PCI/PCIe设备中断都是level触发,并且请求信号为低电平有效 - PCI总线一般只有INTA#到INTD#的4个中断引脚,所以PCI多功能设备的func一般不会超过4个,但是共享中断除外 2 IOMMU 2.1 ARM SMMU v2 Refer to my blog ARM SMMU v2. 2.…

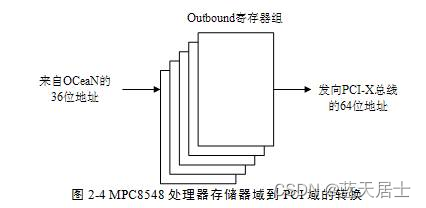

《PCI Express体系结构导读》随记 —— 第I篇 第2章 PCI总线的桥与配置(8)

接前一篇文章:《PCI Express体系结构导读》随记 —— 第I篇 第2章 PCI总线的桥与配置(7) 2.2 HOST主桥

MPC8548处理器的拓扑结构如图2-2所示: 2.2.2 存储器域地址空间到PCI总线域地址空间的转换

MPC8548处理器使用ATMUÿ…

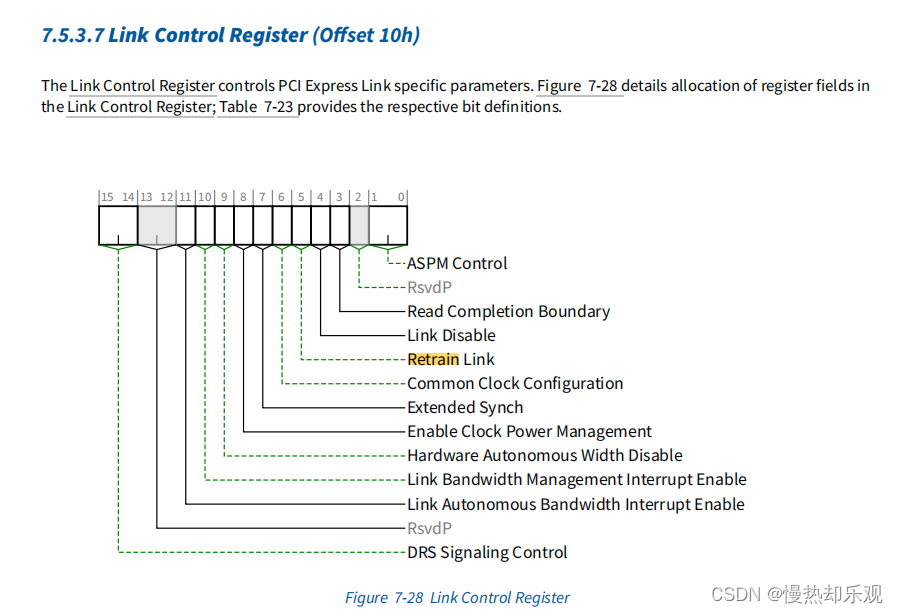

setpci设定PCIe寄存器

PCIe寄存器信息读取、分析、配置 1.获取bdf (bus:device.function)地址2.根据bdf地址抓取pci信息3.结合PCIe Spec对读到的信息进行分析使用setpci修改 1.获取bdf (bus:device.function)地址

在Linux系统下使用命令: l…

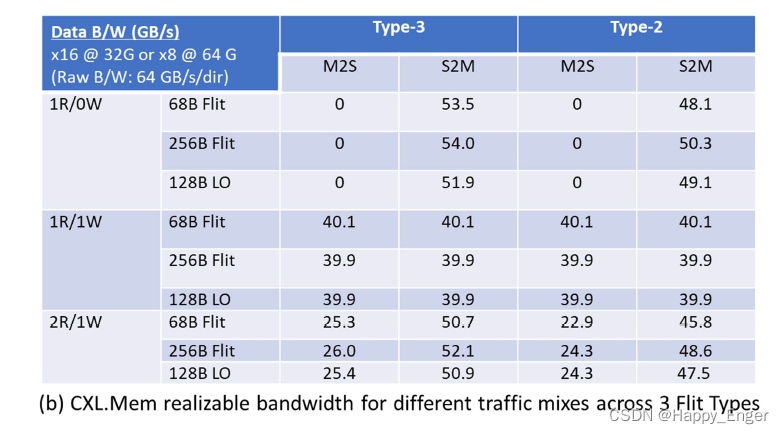

与 PCIe 相比,CXL为何低延迟高带宽?

文章目录 前言1. LatencyPCIE 生产者消费则模型结论Flit 包PCIE/CXL.ioCXL.cace & .mem总结 2. BandWidth常见开销CXL.IO Link efficiencyPCIe Link efficiencyCXL.IO bandwidthCXL.mem/.cache bandwidth 参考 前言

CXL 规范里没有具体描述与PCIe 相比低延时高带宽的原因&…

『CV学习笔记』NVIDIA NVLink和NVSwitch介绍

NVIDIA NVLink和NVSwitch介绍 文章目录 一. 全球最大GPU背后秘密:NVLink和NVSwitch如何实现NVIDIA DGX的超强功力1.1. 单GPU1.2. 双GPU(PCIe和NVLink)1.2.1. PCIe1.2.2. NVLink1.3. GPU \times

【PCIe 5.0 - 10】Memory, I/O, and Configuration Request 规则

下列规则适用于所有 Memory, I/O, Configuration Requests,以下是针对各类请求的附加规则。

除通用 header 字段外,所有 Memory, I/O, 和 Configuration Requests 还包括以下字段: Requester ID[15:0] 和 Tag[9:0],组成 Transact…

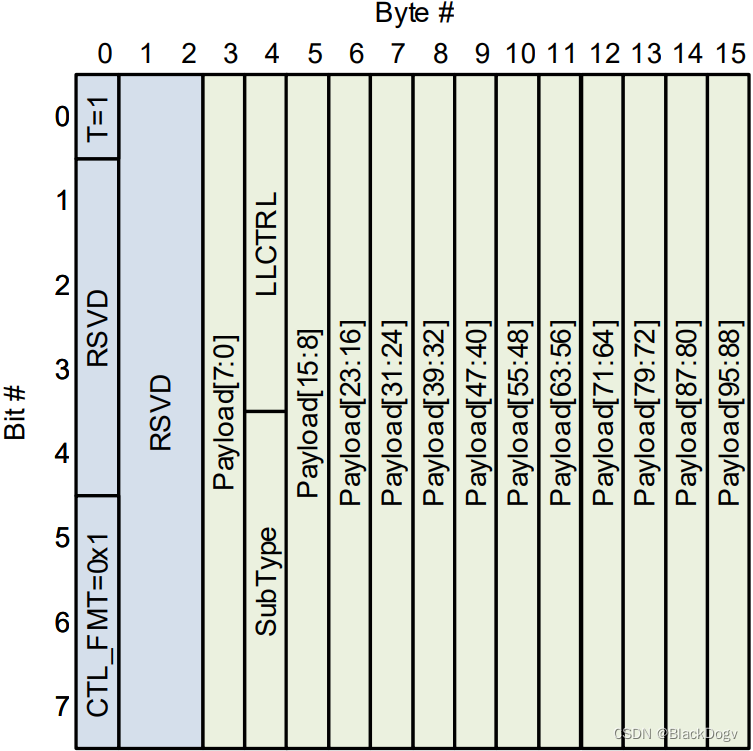

Compute Express Link Link Layers (CXL2.0 Chapter4 )

CXL.io Link Layer 作为Flex Bus Physical layer和cxl.io transaction layer的中间桥梁。 CXL.mem and CXL.cache Common Link Layer CXL.cache 和 CXL.mem Link Layer使用通用的Link Layer

High-Level CXL.cache/CXL.mem Flit Overview CXL.cache/mem flit的大小尺寸固定为52…

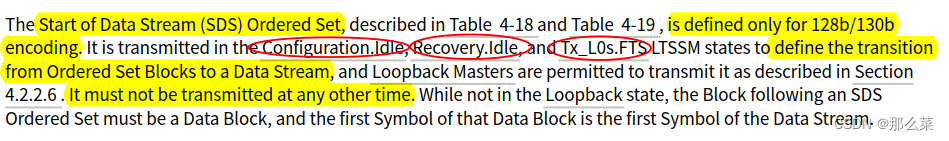

S4.2.4.7 Start of Data Stream Ordered Set (SDS)

一 本章节主讲知识点

1.1 xxx

1.2 sss

1.3 ddd

二 本章节原文翻译

2.1 SDS 数据流开始有序集 SDS 代表传输的数据类型从有序集转为数据流。它会在 Configuration.Idle,Recovery.Idle 和 Tx 的 L0s.FTS 状态发送。Loopback 模式下,主机允许发送 SDS。…

HI3559AV100和FPGA 7K690T的PCIE接口调试记录

1、基本情况 HI3559AV100和690t之间使用pcie2.0 x2接口连接,3559作为RC端,690T作为EP端,驱动使用XDMA。系统主要功能是FPGA采集srio接口过来的图像数据,再通过pcie把数据传递给3559,3559再实现图像数据的存储、AI处理、…

FPGA基于XDMA实现PCIE X4视频采集HDMI输出 提供工程源码和QT上位机程序和技术支持

目录1、前言2、我已有的PCIE方案3、PCIE理论4、总体设计思路和方案5、vivado工程详解6、驱动安装7、QT上位机软件8、上板调试验证9、福利:工程代码的获取1、前言

PCIE(PCI Express)采用了目前业内流行的点对点串行连接,比起 PCI …

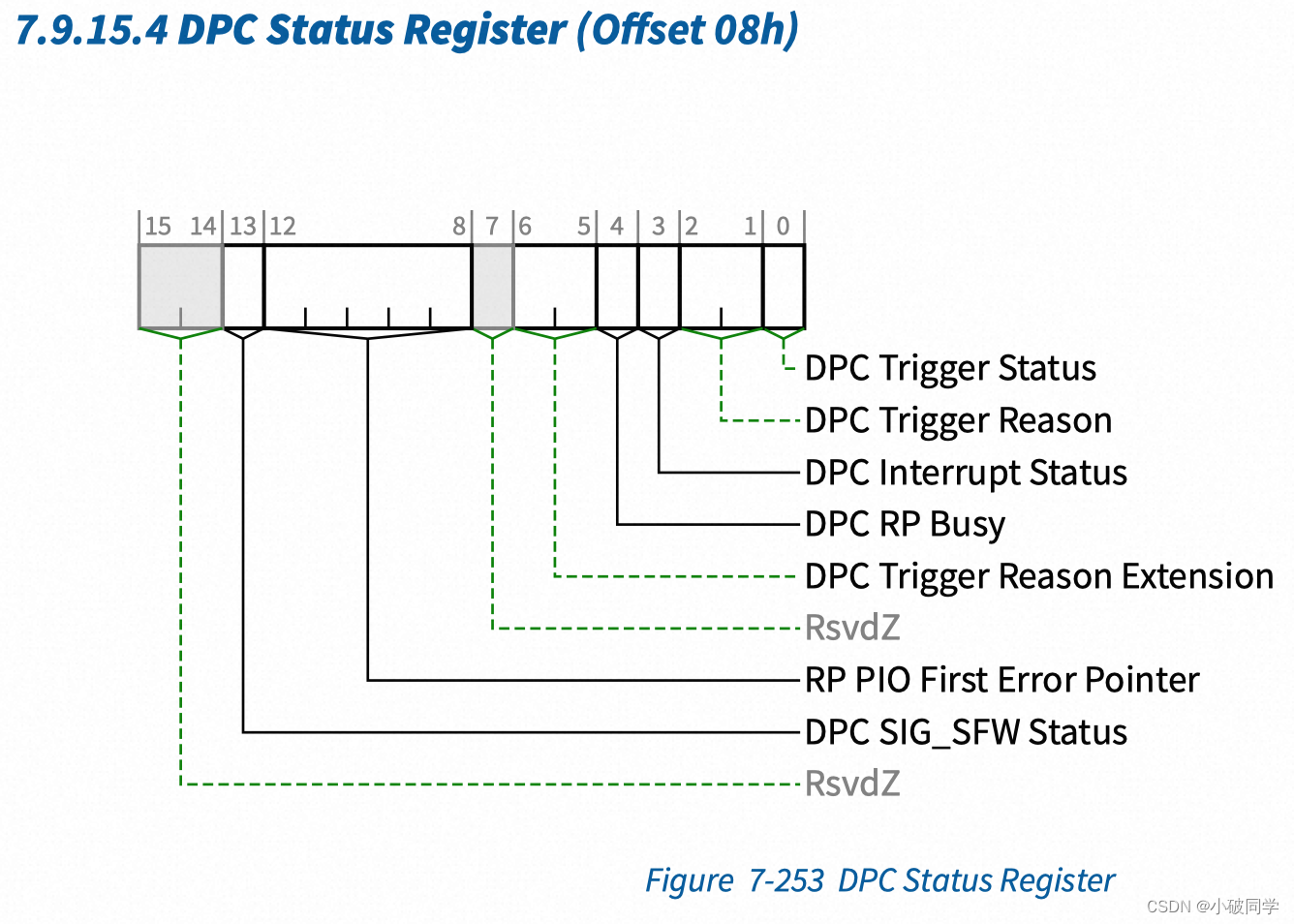

PCIe学习笔记(2)错误处理和AER/DPC功能

文章目录 PCIe ErrorAER (Advanced Error Reporting)DPC (Downstream Port Containment) 处理器上错误通常可分为detected和undetected error。Undetected errors可能变得良性(benign),也可能导致系统故障如silent data corruptions (SDC)。Detected errors则又可分…

DDR与PCIe:高性能SoC的双引擎

SoC芯片无处不在,小到家电控制的MCU,大到手机芯片,我们都会接触到。如今大部分芯片设计公司都在开发SoC芯片,一颗SoC芯片可以集成越来越多的功能,俨然它已成为IC设计业界的焦点。

高性能、高速、高带宽的互联和存储的…

第5代PCIe技术PCIe 5.0详解

前言

PCIe 5.0 第5代PCIe技术PCIe5.0速度是 PCIe 4.0 的两倍,并具有向下兼容性。PCIe 5.0 协议分析仪能够支持 32GT/秒的数据链路速度操作,同时具有卓越的内存、存储容量和分段功能,可捕获更大容量的上行和下行流量。什么是 PCIe 5.0&#x…

《PCI Express体系结构导读》随记 —— 第II篇 第4章 PCIe总线概述(5)

接前一篇文章:《PCI Express体系结构导读》随记 —— 第II篇 第4章 PCIe总线概述(4) 4.1.2 PCIe总线使用的信号 PCIe设备使用两种电源信号供电,分别是Vcc与Vaux,其额定电压为3.3V。其中Vcc为主电源,PCIe设备…

海思芯片pcie启动——pcie_mcc驱动框架的booter程序分析

1、booter程序介绍 (1)源码目录:pcie_mcc/multi_boot/example/boot_test.c; (2)调用命令:./booter start_device; (3)booter程序的作用:在主片将pcie启动相关的驱动加载完成后,调用booter来引导从片pcie启动; 2、主片引导从片启动的过程 (1)调用pcie启动相关驱动,知道当…

PCIE链路初始化训练

PCIE链路初始化&训练概述Ordered Sets In Link TrainingLTSSMDetect状态Polling状态配置状态L0状态恢复状态动态带宽变化配置相关寄存器链路初始化过程是指链路从Power-On或者复位后到完全工作L0状态的过程。概述

链路初始化和训练是由物理层控制的纯硬件过程,…

![[SSD科普之2] SATA、mSATA、M.2、M.2(NVMe)、PCIE固态硬盘接口详解](https://img-blog.csdnimg.cn/img_convert/b64ffa9ac2b249c8a41c8b4c3e70b1ec.png)

![[SSD科普之1] PCIE接口详解及应用模式](https://img-blog.csdnimg.cn/img_convert/7316898ce6464d7ca1811808269a4b0d.png)